Q. shafiee, T. Dragicevic, J. C. Vasquez, and J. M. Guerrero, "Modeling, Stability Analysis and Active Stabilization of Multiple DC-Microgrid Clusters," in Proc. IEEE International Energy Conference (EnergyCon'14), 2014.

# Modeling, Stability Analysis and Active Stabilization of Multiple DC-Microgrid Clusters

Qobad Shafiee, Tomislav Dragicevic, Juan C. Vasquez, and Josep M. Guerrero Institute of Energy Technology, Aalborg University (AAU)

Aalborg East DK-9220, Denmark

Email: qsh, tdr, juq, joz@et.aau.dk

Abstract—DC microgrids (MGs), as an alternative option, have attracted increasing interest in recent years due to many potential advantages as compare to the ac system. Stability of these systems can be an important issue under high penetration of load converters which behaves as constant power loads (CPLs), and more especially during interconnection with other MGs, creating dc MG clusters. This paper develops a small signal model for dc MGs from the control point of view, in order to study stability analysis and investigate effects of CPLs and line impedances between the MGs on stability of these systems. This model can be also used to synthesis and study dynamics of control loops in dc MGs and also dc MG clusters. An active stabilization method is proposed to be implemented as a dc active power filter (APF) inside the MGs in order to not only increase damping of dc MGs at the presence of CPLs but also to improve their stability while connecting to the other MGs. Simulation results are provided to evaluate the developed models and demonstrate the effectiveness of proposed active stabilization technique.

Index Terms—Microgrid (MG), dc microgrid clusters, constant power load, stability analysis, small signal model, active damping methods.

#### I. INTRODUCTION

DC microgrids (MGs) are researched recently to facilitate integrating of modern electronic loads and alternative energy sources with dc output type such as photovoltaic (PV) system, fuel cell, and energy storages (e.g., secondary battery and super capacitor) [1]–[9], [14]. Normally, dc MGs are proposed for power supply of applications with sensitive and/or dc loads like consumer electronics, electric vehicles, naval ships, space crafts, submarines, industrial power systems, telecom systems and rural areas [1] to be benefited from increased power quality, and higher reliability and efficiency.

These systems have several advantages summarized as 1) the conversion losses from sources to loads are reduced, thus enhancing the system efficiency; 2) there is no need for control of frequency and phase, reactive power, and power quality which are all big challenges in ac MGs. Furthermore, synchronization requirements for connection of sources and ESSs to the bus and the main grid are not an issue in dc MGs; 3) in the grid connection mode, any blackout or voltage sag that may happen from the grid side does not affect the units inside the dc MG.

Although there is a significant increase of dc MG projects nowadays, we can still find lack of study about modelling, stability analysis, and control of these systems, especially in the case that they are connected to the other MGs to create dc

MG clusters. Modeling of power electronic systems has been addressed in several research works [11]–[13], however, yet there is no general model for dc MGs based on the introduced hierarchical control loops [10].

Stability of dc MGs is influenced under high penetration of tightly regulated power converters used to interface distributed resources and loads [15]. In these systems, load converters and batteries during regulated charging mode behave as constant power loads (CPL), thus extracting constant power from the MG bus [9]. CPLs introduce a negative incremental resistance feature, which reduces the system stability [13]–[16]. Moreover, interconnecting dc MGs together in order to create MG clusters tends to destabilize the system depending on the line impedance between the MGs.

Several methods have been proposed to compensate the CPLs effect in power electronic converters and MG applications [13], [15]–[17]. However, no research work has been done to improve the stability of MGs while they are connected as MG clusters. To overcome the negative impedance instability problem of CPLs, both passive and active methods have been presented. Passive methods are basic ones that employ damping passive element(s) in the (output LC filter of) source converter to reshape its impedance. While active damping strategies [14]–[17] use the virtual control loops to improve the stability, offering higher efficiency and reliability.

This paper develops a small signal model for interconnected multiple dc MGs from the control point of view. This model is used to design the control loops and study of their dynamics. It is also used to study small signal stability analysis and explore how stability is affected by CPLs and line impedances between the MGs. The influence of communication delay on the system stability can be also evaluated using this model. Block diagrams of the model are drawn to facilitate the analysis. The ultimate goal is to design an active stabilization loop in order to improve the stability of MG clusters at the presence of CPLs and connection of MGs.

#### II. DC MICROGRID CONFIGURATION

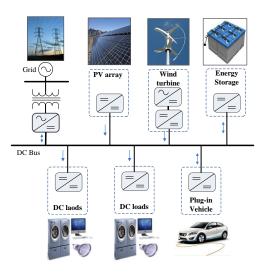

Normally a dc MG consists of distributed energy resources (DER) and energy storage systems (ESS) which are supplying sort of electronic loads through a common dc bus. Fig. 1 shows general configuration of a low-voltage dc (LVDC) microgrid. DERs used in a LVDC microgrid can be various types such as

Fig. 1. Typical configuration of a low-voltage dc microgrid.

photovoltaic (PV) arrays, fuel cells, wind-turbine (WT) generators, and microturbines. PV and FC are more appropriate to be used in dc MGs since they produce dc voltage. However, WT and microturbine which generate voltage with varying frequency, require conversion to be connected to the dc bus and used in dc MGs.

On the other hand, due to transient response of sources, and the fact that they cannot be always available (in the case of RESs), ESSs are mandatory to be connected to the dc MG. Furthermore, they can be used for ancillary services like voltage regulation, power quality improvement and emergency power supply. Normally secondary batteries, super capacitors, and flywheels are used as an ESS. Batteries and capacitors can be directly connected to the dc bus, but flywheels are connected through a machine and a converter [6]. However, it is desired to connect the ESSs to the dc bus through converters in order to supply high reliable power to the loads.

DERs and ESSs are connected to a common bus establishing a dc MG. The common bus is linked to the sources through the power electronic interfaces. Depending on the source type and voltage, there could be one or two stages of power conversion as shown in Fig. 1. Nevertheless, last conversion stage is ordinarily a dc-dc converter. To connect different sources and loads to the dc MG, different dc-dc converters with different characteristics must be used [18]. The structure of these converters is simpler than ac-dc one, which results in higher efficiency and lower cost. Furthermore, comparing to the ac MG, dc one requires fewer power converters, and it is easier interfaced to the sources.

#### III. HIERARCHICAL CONTROL OF DC MICROGRIDS

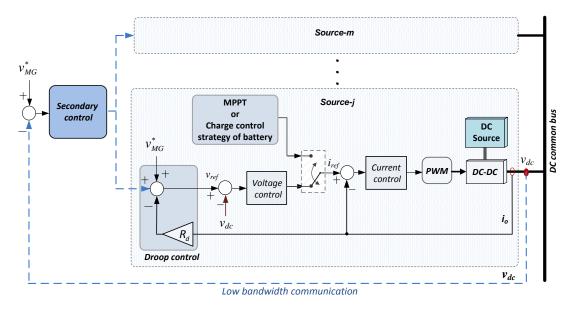

A hierarchical multilevel control strategy has been introduced for MGs with three level of primary, secondary and tertiary control [10]. For dc MGs, primary control is employed locally for every source inside the MG in order to regulate the current injection into the common bus automatically. Inner control loops are performed to regulate voltage and current while maintaining the system stable. These loops ensure that

the actual voltage of each source is equal to its reference value (see Fig. 2). In order to connect a number of voltage source converter (VSC) based sources in parallel, a virtual output impedance loop called droop control is needed. This control loop shares current between the units accordingly, and reduces the circulating current when the MG units voltages are different. Moreover, it improves the dynamic performance of the source output voltage [10]. This control loops creates appropriate voltage reference for the voltage inner loop as follows

$$v_{ref} = v_{MG}^* - R_d \cdot i_o \tag{1}$$

with  $v_{MG}^{*}$  being MG voltage reference,  $i_{o}$  is the output current and  $R_{d}$  is the virtual resistance. To ensure low voltage deviation, low value of droop gain  $R_{d}$  is used. The larger droop gains, the more voltage deviation of the dc MG and better load sharing.

Although it has been proved that droop control is an efficient method for parallel operation of sources inside the MG, it is not the best solution for the RESs using the droop control and participating always in the voltage support. It is normally preferred to extract maximum available power from RESs whenever is possible, using maximum power point tracking (MPPT) algorithms. Moreover, appropriate methods should be considered in order to recover the state-of-charge (SOC) of the connected battery inside the dc MG. When battery is discharged, constant voltage charging is normally applied [9]. It is worth mentioning that MPPT control of RESs and charging control of batteries act as a constant power source (CPS) and constant power load (CPL), respectively. Therefore, both control strategies are modeled as an adjustable current reference to produce set-point for the current inner loop as shown in Fig. 2. To sum up, combination of mandatory droop control units (at least one for each MG) and optional CP units (CPS or CPL) is introduced as primary control of dc MGs.

The primary control introduces the deviation of the common dc bus voltage, due to disbalance between power consumption and production. In order to restore the voltage of MG bus to nominal value, a centralized voltage secondary control can be implemented. This control strategy which is usually realized with standard PI controller removes the voltage deviations inside the MG by sending an appropriate set-point (as shown in Fig. 2) to the droop control sources using a low bandwidth communication (LBC). This signal changes the voltage reference of droop unit(s) accordingly by shifting the droop line up and down. This control loop could be also implemented in a distributed way over the MG units using LBC to avoid having a single point failure [19].

On the other hand, in case that the MG is connected to the other dc MGs or another dc bus, the concept of tertiary control must be employed in order to control the power flow.

#### IV. MODELING OF DC MICROGRIDS

In this section a generalized model is presented for dc MGs as well as interconnected dc MGs considering aforementioned control loops. First, a simplified model is presented for a buck

Fig. 2. Primary and secondary control of dc MGs.

converter as a base for implementing control loops, and then the control loops are modeled one by one in order to develop a general small signal model for dc MGs. Finally, the obtained model is extended for interconnected dc MGs.

#### A. Mathematical Model of a Buck Converter

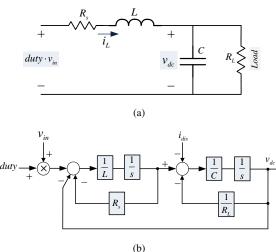

For simplicity, a buck converter that supplies a dc load through a series LC filter is analyzed without losing any generalization. Here, an average method is used so that only the averaged dynamics has been considered and the high frequency switching dynamics have been neglected. The simplified buck converter with the corresponding LC circuit supporting a dc load is modelled as shown in Fig. 3(a). The dc load can be combination of resistive electronic loads and negative resistance of CPLs. The mathematical model of the buck converter can be described as follows [16]:

$$\begin{cases}

L\frac{di_L}{dt} = (duty \cdot v_{in}) - v_{dc} - i_L \cdot R_s \\

C\frac{dv_{dc}}{dt} = i_L - \frac{v_{dc}}{R_L}

\end{cases}$$

(2)

with  $R_L$  being the total equivalent resistance seen by the system. C, L and  $R_s$  are the converter output capacitance, inductance and inductor losses, respectively. Then, the corresponding transfer function is given as

$$\frac{v_{dc}(s)}{duty \cdot v_{in}(s)} = \frac{1}{LC \cdot s^2 + (R_sC + \frac{L}{R_I}) \cdot s + (1 + \frac{R_s}{R_I})}$$

(3)

The location of the poles of the LC filter should be investigated in order to study the stability of the buck converter. From denominator of (3) the poles are determined as

$$p_{1,2} = \frac{-(R_sC + \frac{L}{R_L}) \pm \sqrt{(R_sC + \frac{L}{R_L})^2 - 4LC \cdot (1 + \frac{R_s}{R_L})}}{2LC}$$

(4)

Fig. 3. Representing the averaged dynamics of a buck converter. (a) equivalent circuit, (b) block diagram

To have a stable system,  $R_sC+\frac{L}{R_L}$  should be positive since in the practical cases  $|R_L|>R_s$ . It is obvious that if  $R_L$  is negative due to the existence of CPLs, the system would inherently be unstable. The mathematical model of (2) is represented as a block diagram in Fig. 3(b).

#### B. Current and Voltage Regulators

A functional control diagram of a dc-dc converter inside a MG, includes primary and secondary control, is presented in Fig. 2. As shown in this figure, the inner current control loop is employed to regulate the current of dc-dc converter and voltage controller which generates the current reference  $(i_{ref})$  for current loop, regulates dc bus voltage. Normally, proportional-integral (PI) controllers are used in these inner loops. To design the inner control loops and study stability analysis a small signal model is needed.

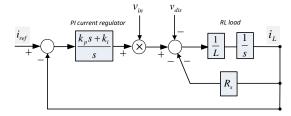

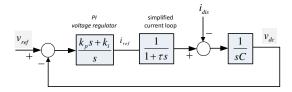

Using the model derived in the previous subsection, a

Fig. 4. Block diagram of the current control loop.

Fig. 5. Block diagram of dc voltage control loop.

simplified current control loop is developed and the block diagram is presented in Fig. 4. A reduced order diagram can be constructed using the reasonable simplification in which the  $R_s - L$  elements and inner current loop are considered to follow imposed references. This way, the current loop can be reduced to a first-order delay to simplify the analysis and derive the analytical expressions of current regulators [11]. According to [11], the dominant pole of the  $R_s$  – L load can be canceled by setting the integral time constant of the PI current regulator equal to that of the load. Therefore, the simplified current control loop shown in Fig. 4 can be represented as a first-order transfer function with time constant of three times higher than the system sampling time. Moreover, to improve the disturbance rejection capability, the time constant of the current regulator can be selected to be fifteen times higher than sampling time of the system. It is worth noting that the bandwidth of the current PI controller is normally considered approximately twenty times higher than the system sampling time [11].

Similarly, the voltage control loop can be modeled with the block diagram of Fig. 5. The block diagram shows that the current control loop is modeled using the first order transfer function. As above mentioned time constant of the first order transfer function is three times higher than the system sampling time. Since sampling frequency for dc systems is practically high, the dominant pole of the simplified current loop is too far, thus one can note that the simplified current loop (first order transfer function) can be cancel out from the model for more simplification.

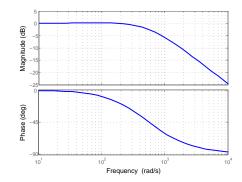

A system with sampling time  $T_s=0.1\ ms,\ L=1.8\ mH,\ R_s=2\ m\Omega,$  and  $C=2.2\ mF$  was simulated and tested using the developed model. The bode plot with the amplitude and phase responses of the voltage loop is presented in Fig. 6. Assuming bandwidth of 500 Hz for the current loop, parameters of PI voltage controller was tuned using the proposed model so that bandwidth of voltage loop is approximately 100 Hz (see Fig. 6).

Fig. 6. Frequency response of the closed loop voltage regulator.

Fig. 7. Block diagram of primary control loop.

#### C. Primary Control

As aforementioned, sources inside a dc MG can use two different control strategies, where every one of them has particular effect on stability of the system. RESs can be regulated by droop control or controlled with MPPT algorithms (CPSs), while batteries can be charged in regulated manner (CPLs) or be regulated by droop as well [9]. An ideal CPS is modeled as a positive incremental resistance and negative current source. Whereas, a complete expression for current of a perfect CPL is as follows [16]:

$$i = \frac{1}{R_{CPL}} \cdot v + I_{CPL} \tag{5}$$

where  $R_{CPL}=-\frac{V^2}{P_{CPL}}$  and  $I_{CPL}=2\cdot\frac{P}{V}$  for a given operating point of  $I=\frac{P}{V}$ .

Therefore, according to (5), a perfect CPL can be represented as a negative resistance in parallel with positive current source. The negative resistance of CPLs decreases damping of the system, while the positive resistance of CPSs enhances the stability. Moreover, the positive and negative constant current sources have no effect on the stability [17]. Taking the mentioned considerations into account, we can conclude that by modelling droop control loop and considering CPLs in the model, small signal stability analysis of the primary control is covered without losing generalization. Thus, if stability can be ensured in this worse case, MG should be stable in all other cases.

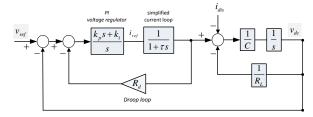

Fig. 7 presents block diagram of primary control for a dc-dc converter inside a MG. In this diagram,  $R_d$  is virtual resistance of droop loop and  $R_L$  represents equivalent load that can be combination of a resistive electronic load with positive or negative resistances produced by CPSs or CPLs.

By extracting the state space model of the system from

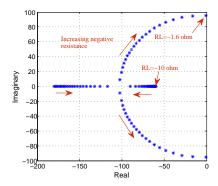

Fig. 8. Family of the closed-loop eigenvlues of the system as the negative resistance of a CPL increases.

Fig. 9. Small signal model of two interconnected MGs.

the presented block diagram, impact of negative resistance of CPLs, virtual resistance, and other parameters of control loops on the system stability can be easily investigated. Notice that in this model the simplified current loop is assumed to be removed for more simplification, since its dominant pole is quite far from the others as explained above.

Using the extracted state space model, the root locus graph is plotted, presented in Fig. 8, under gradual change of the negative resistance of a CPL from  $-10~\Omega$  to  $-1.6~\Omega$ . As can be observed, the close loop eigenvalues travel to the right hand side of the s plane as negative resistance of CPL increases, which indicates unstable conditions for the system. Impact of other parameters of system on the stability can be studied similarly.

## V. SMALL SIGNAL MODELING OF INTERCONNECTED DC MICROGRIDS

DC MGs can be made more reliable by interconnecting to the other MGs, creating MG clusters. This way, each dc MG will be able to absorb/inject power from/to the other MGs. Nevertheless, stability is influenced depending on the ratio of the resistance and inductance of the interconnected line.

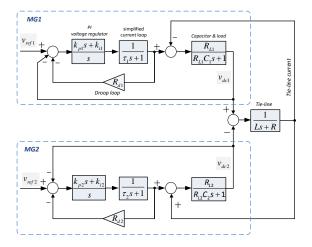

The developed model for dc MGs can be easily expanded for multiple dc MG clusters. Block diagram representation of two interconnected MGs with the implemented droop-control

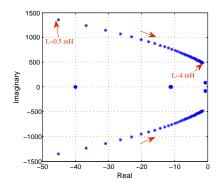

Fig. 10. Family of the closed-loop eigenvalues of the interconnected MGs for different value of line inductance.

is shown in Fig. 9. Here, L and R are the inductance and resistance of interconnected line between MGs, respectively. As the block diagram shows, tie-line current is added to the input of RC filter as a disturbance. Using this model, it is possible to study small signal stability analysis. Moreover, impact of both CPLs and interconnection line parameters can be investigated. For simplicity, only one source is considered inside each MG to be modeled which can represent the MG model generally. However, model of other MG units can be eassily added in case it is needed. Similarly, secondary and tertiary control loops can be added to the presented model.

Using the presented block diagram, a state space model is extracted accordingly to study the behavior of eigenvalues and evaluate impact of different parameters on the system stability. Fig. 10 shows the behavior of system eigenvalues when inductance of interconnected line changes between  $0.5\ mH$  and  $4\ mH$ .

#### VI. PROPOSED ACTIVE STABILIZATION METHOD

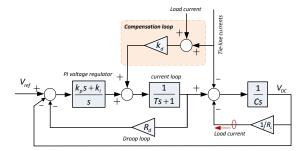

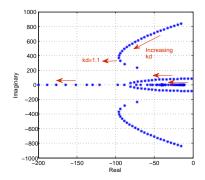

When connecting MGs together, stability of system may be influenced depending on the parameters of interconnected line. It is shown that if the line inductance becomes bigger and the line resistance gets smaller than some special values, the system moves toward unstable region. In this section, a feed-forward loop is proposed as an active damping loop to increase damping and improve stability of the system as shown in Fig. 11. The aim of this loop is to reject the impact of disturbances, which can be due to either load changes and/or tie-line current, on the system. In this method, as diagram of Fig. 11 presents, the disturbance currents are measured, and sent to the compensation loop through a communication link, then it should be feed-forwarded to the input of current regulator loop using compensation gain  $(k_d)$ . Here, sum of load current and tie-line current is considered as disturbance input for feed-forward loop, in order to cancel the impact of both disturbances. Since the dc-bus voltage is influenced by the disturbances, the utilization of proposed method removes the oscillations in the dc voltage. The principle of rejecting the impact of the disturbances is first to calculate the compensation gain. As shown in Fig. 12, root-locus analysis is applied using the extracted state space model form the block diagram, in order to obtain the feed=forward compensation gain. As

Fig. 11. Block diagram representing implementation of proposed feed-forward compensation loop.

Fig. 12. Family of the closed-loop eigenvlues of the system as the feedforward compensation gain  $(k_d)$  increases.

this figure illustrates, eigenvalues of the system moves toward stable region by increasing  $k_d$ . It is seen that the optimal value for compensation gain is  $k_d = 1.1$ . Parameters shown in Table I are used for this simulations.

Since the proposed loop needs high speed communication to receive the tie-line current measurements, it does not make sense to implement it on the all units inside the MGs. Therefore, it is proposed to dedicate one unit with implemented compensation loop as a dc active power filter (APF) to stabilize the whole MG.

### VII. SIMULATION RESULTS

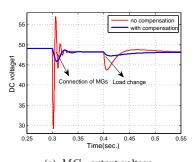

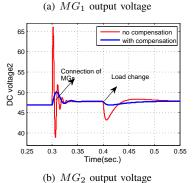

Simulation results of two interconnected dc MGs are presented in order to show the feasibility of developed model and evaluate the proposed active stabilization method. MGs are connected through high resistive-inductive lines supporting 10  $\Omega$  and 6  $\Omega$  loads, respectively. For the simulation, the MGs voltage was selected at 48 V. Other parameters of system can be found in Table I. Fig. 13 shows the effectiveness of proposed active damping loop while primary control is acting over two interconnected MGs. Results show dc output voltage of MGs for different scenarios with and without compensation loop. As seen, MGs are connected together at t=0.3 s, while the loads suddenly decrease to half at the middle of simulation. It can be observed that the proposed active damping method is able to reject the current disturbances produced by both load changes and connection of MGs.

TABLE I ELECTRICAL SETUP AND CONTROL SYSTEM PARAMETERS

| Parameter                       | Symbol        | Value         |

|---------------------------------|---------------|---------------|

| Electrical parameters           |               |               |

| dc power supply                 | Vin           | 100 V         |

| Output capacitance              | C             | 2.2e-3 F      |

| Converter inductances           | L             | 1.8e-3 H      |

| Inductor+switch loss resistance | $R_s$         | $0.2 \Omega$  |

| Virtual resistance              | $R_d$         | $0.5 \Omega$  |

| Switching frequency             | $f_{sw}$      | 10 kHz        |

| Primary Control                 |               |               |

| Reference voltage               | $v_{MG}^*$    | 48 V          |

| Proportional current term       | $k_{pi}^{MG}$ | 5             |

| Integral current term           | $k_{ii}$      | 994           |

| Proportional voltage term       | $k_{pv}$      | 1.2           |

| Integral voltage term           | $k_{iv}$      | 97            |

| tie-line parameters             |               |               |

| Line inductance                 | L             | 1.8e-3 mH     |

| Line resistance                 | R             | $0.05 \Omega$ |

| tie-line param                  | eters L       | 1.8e-3 mI     |

Fig. 13. Effectiveness of proposed active stabilization method in rejecting

#### VIII. CONCLUSION

disturbances.

This paper has addressed small signal modeling and stability issues in dc MGs and dc MG clusters. A model was developed to design and synthesize control loops of dc MGs. Using this model, small signal stability analysis of dc MGs and then interconnected dc MGs is possible. Impact of negative incremental resistance caused by CPLs and parameters of interconnected line between MGs was studied. An active-damping method which is a feed-forward compensation loop, was proposed to stabilize dc MG clusters when they are connected. This active damping method can be also used to stabilize the dc/dc converters loaded by CPLs. As this compensation loop needs

high speed communication to receive the disturbance currents, it was proposed to allocate one unit inside each MG as an active power filter. To verify the effectiveness of the developed model and proposed active damping method, some simulation results was carried out.

#### REFERENCES

- [1] R. S. Balog and P. T. Krein, "Bus selection in multibus DC microgrids", IEEE Trans. Power Electron., vol. 26, no. 3, pp. 860–867, Mar. 2011.

- [2] Kwasinski, A., "Quantitative Evaluation of DC Microgrids Availability: Effects of System Architecture and Converter Topology Design Choices," IEEE Trans. Power Electron., vol.26, no.3, pp.835,851, March 2011.

- [3] K. Sun, L. Zhang, Y. Xing, and J. M. Guerrero, "A distributed control strategy based on DC bus signaling for modular photovoltaic generation systems with battery energy storage", IEEE Trans. Power Electron., vol. 26, no. 10, pp. 3032–3045, Oct. 2011.

- [4] S. Anand, B. G. Fernandes, J. M. Guerrero, "Distributed Control to Ensure Proportional Load Sharing and Improve Voltage Regulation in Low-Voltage DC Microgrids", IEEE Trans. Power Electron., vol.28, no.4, pp.1900–1913, April 2013.

- [5] X. Lu, J. M. Guerrero, K. Sun, J. C. Vasquez, "An Improved Control Method for DC Microgrids Based on Low Bandwidth Communication with DC Bus Voltage Restoration and Enhanced Current Sharing Accuracy", IEEE Trans. Power Electron., Early access, 2013.

- [6] D. Salomonsson, L. Soder, and A. Sannino, "Protection of low-voltage DC microgrids", IEEE Trans. Power Del., vol. 24, no. 3, pp. 1045–1053, Jul. 2009.

- [7] H. Kakigano, Y. Miura, and T. Ise, "Low-voltage bipolar-type DC microgrid for super high quality distribution", IEEE Trans. Power Electron., vol. 25, no. 12, pp. 3066–3075, Dec. 2010.

- [8] T. Dragicevic, J. M. Guerrero, J. C. Vasquez, "A Distributed Control Strategy for Coordination of an Autonomous LVDC Microgrid Based on Power-Line Signalling", IEEE Trans. Ind. Electron., Early access, 2014.

- [9] T. Dragicevic, J. M. Guerrero, J. C. Vasquez, D. Skrlec, "Supervisory Control of an Adaptive-Droop Regulated DC Microgrid With Battery Management Capability", IEEE Trans. Power Electron., vol. 29, no. 2, pp. 695–706, Feb. 2014.

- [10] J. M. Guerrero, J. C. Vasquez, J. Matas, M. Castilla, L. G. D. Vicua, and M. Castilla, "Hierarchical Control of Droop-Controlled AC and DC Microgrids-A General Approach Toward Standardization", IEEE Trans. Ind. Electron., vol.58, no.1, pp.158–172, Jan. 2011.

- [11] V. Blasko and V. Kaura, "A New Mathematical Model and Control of a Three-Phase ACDC Voltage Source Converter", IEEE Trans. Power Electron., vol. 12, no. 1, pp. 116–123, Jan. 1997.

- [12] G. R. Yu, J. S. Wei, "Modeling and Control of a Bi-directional Inverter for DC Microgrids", IEEE Proceedings of International Conference on System Science and Engineering, June 2011.

- [13] A. Emadi, A. Khaligh, C. H. Rivetta, and G. A. Williamson, "Constant power loads and negative impedance instability in automotive systems: Definition, modeling, stability, and control of power electronic converters and motor drives", IEEE Trans. Veh. Technol., vol. 55, no. 4, pp. 1112– 1125, Jul. 2006.

- [14] A. Kwasinski and C. Onwuchekwa, "Dynamic behavior and stabilization of DC micro-grids with instantaneous constant-power loads", IEEE Trans. Power Electron., vol. 26, no. 3, pp. 822–834, Mar. 2011.

- [15] A. A. A. Radwan, Y. A. I. Mohamed "Linear Active Stabilization of Converter-Dominated DC Microgrids", IEEE Trans. Smart Grid, vol. 3, no. 1, pp. 203–216, Mar. 2012.

- [16] A. M. Rahimi and A. Emadi, "Active damping in DC/DC power electronic converters: A novel method to overcome the problems of constant power loads", IEEE Trans. Ind. Electron., vol. 56, no. 5, pp. 1428–1439, 2009.

- [17] A. Rahimi, G. Williamson, and A. Emadi, "Loop-cancellation technique: A novel nonlinear feedback to overcome the destabilizing effect of constant-power loads", IEEE Trans. Veh. Technol., vol. 59, no. 2, pp. 650–661, Feb. 2010.

- [18] D. Boroyevich, I. Cvetkovic, D. Dong, R. Burgos, W. Fei; F. Lee, "Future electronic power distribution systems a contemplative view", OPTIM 2010, pp.1369–1380, 20-22 May 2010.

- [19] Q. Shafiee, J. M. Guerrero, J. Vasquez, "Distributed Secondary Control for Islanded MicroGrids - A Novel Approach", *IEEE Trans. Power Electron.*, vol.29, no.2, pp.1018–1031, Feb. 2014.